### Cell-Based IC Physical Design & Verification SOC Encounter

# Advisor : 李昆忠Presenter : 蕭智元

### **VLSI System Design**

Reference: SOC Encounter Training Manual, 2007, edited by CIC.

< / ∃ ⇒

### Introduction

- We'll use some EDA tools to transform synthesized design to layout

- Tools

- SOC Encounter: Floorplanningand APR

- icfb: Cell replacement with layout

- Calibre: DRC, LVS

### **Prepare File**

- Unix% cp -r /home4/classuser/sys0701/sys0701ta1/SOCE .

- Library

- Physical Library (.lef)

- Timing Library (.lib)

- User Data

- Gate-Level netlist (.v)

- SDC constraints (.sdc)

- IO constraint (.ioc)

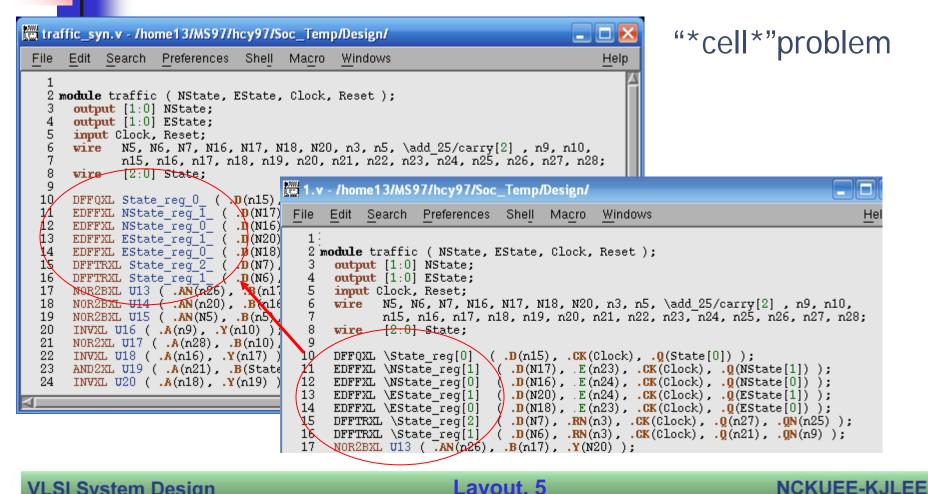

### Gate-Level netlist (1/3)

- Synthesized RTL code

- -"assign" statement is not allowed.

- To solve this, typing

"set\_fix\_multiple\_port\_nets-all -buffer\_constants" in command window before compile.

-"\*cell\*"problem. To solve this, "change\_names -rule verilog-verbose -hierarchy" in command window after compile.

### Gate-Level netlist (2/3)

**VLSI System Design**

### Gate-Level netlist (3/3)

DFFQXL State\_reg\_0 ( .D(n15), .CK(Clock), .Q(State[0]) ); EDEEXI MState reg\_1 ( .D(N17) E(n23) CK(Clock) .O(MState[1])

module CHIP( P0\_NState, P0\_EState, PI\_Clock, PI\_Reset );

output [1:0] P0\_NState;

output [1:0] P0\_EState;

input PI\_Clock, PI\_Reset;

wire [1:0] WIRE\_NState;

wire [1:0] WIRE\_EState;

```

wire WIRE_Clock, WIRE_Reset;

traffic traffic( .NState(WIRE_NState), .EState(WIRE_EState), .Clo

PDIDGZ PAD_Clock ( .PAD(PI_Clock), .C(WIRE_Clock));

PDIDGZ PAD_Reset ( .PAD(PI_Reset), .C(WIRE_Reset));

PD002CDG PAD_N0 ( .I(WIRE_NState[0]), .PAD(P0_NState[0]));

PD002CDG PAD_N1 ( .I(WIRE_NState[1]), .PAD(P0_NState[1]));

PD002CDG PAD_E0 ( .I(WIRE_EState[0]), .PAD(P0_EState[0]));

PD002CDG PAD_E1 ( .I(WIRE_EState[1]), .PAD(P0_EState[1]));

endmodule

```

When Verilogfile is ready

Put all verilogfile (CHIP.v) into SOC\_tutor/vlog

Adding I/O pads into CHIP.v

–input pad : PDIDGZ

–output pad : PDO02CDG

#### **VLSI System Design**

#### Layout. 6

**SDC Constraint**

### Make use of the dc constraint

### • Make sure the port name

1 set sdc version 1.2 3 create\_clock -name Clock -period 5 -waveform {2.5 5} [get\_ports PI\_Clock] 4 set\_operating\_conditions -max slow -max library slow -min fast -min library fast traffic.dc - /home13/MS9775cy97/Soc Temp/Design/ 6 remove wire load model 7 set max area  $600\overline{0}$ 8 set max dynamic power 0 uw Edit Search Preferences Shell Macro Windows File 9 set max leakage power 0 uw 10 set max total power 0 uw 7 # Set the current design # 11 set max fanout 2 [current design] 12 set max transition 0.3 [current design] 8 current design traffic 13 set fix multiple port nets -all\_buffer constants 10 create\_clock -period 5 -waveform (2.5 5) [get ports Clock] 14 set\_load -pin\_load 0.001241 [get\_ports {PO\_NState[1]}] 15 set\_load -pin\_load 0.001241 [get\_ports {PO\_NState[0]}] 1 set operating conditions -max slow \max library slow \ 16 set load -pin load 0.001241 [get ports (PO EState[1])] -min fast -min library fast 17 set load -pin load 0.001241 [get ports {PO EState[0]}] 15 remove wire load model 14 sec max area 6000 18 15 set max dynamic power 0 uw 19 set clock latency 1 [get clocks Clock] 16 set\_max\_leakage\_power 0 uw 20 set clock latency -source 0 [get clocks Clock] 17 set max total power 0 uw 21 set\_clock\_uncertainty 0.1 [get clocks Clock] 18 set\_max\_fanout 2 [corrent\_design] 22 set dont touch network [get clocks Clock] 19 set max transition 0.3 (current design) 23 set fix hold [get clocks Clock] 20 set fix multiple port nets all -buffer constants 24 set clock transition -rise 0.3 [get clocks Clock] 21 set\_load -pin\_load 0.001241 (get\_ports {NState[1]}] 25 set\_clock\_transition -fall 0.3 [get\_clocks Clock] 22 set load -pin load 0.001241 [get ports {NState[0]}] 26 set max delay 2 -from [get ports PI Clock] -to [list [ 23 set\_load -pin\_load 0.001241 [get\_ports {EState[1]}] 27 [get ports {PO NState[0]}] 28 set max delay 2 -from [get ports PI Clock] -to [list [ 24 set load -pin load 0.001241 [get ports {EState[0]}] NCKUEE-KJLEE VLSI System Design Lavout. 7

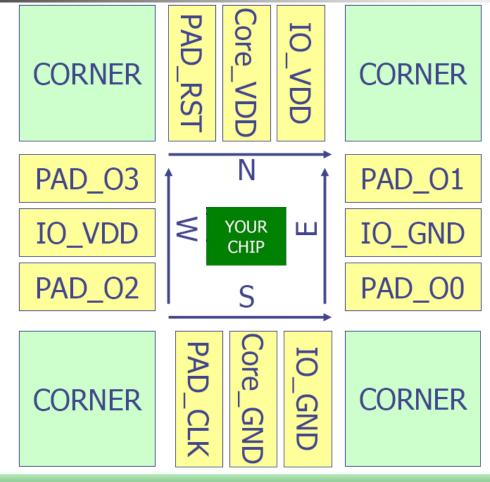

### IO Constraint (1/3)

**VLSI System Design**

### IO Constraint (2/3)

Pad:CORNER0NWPad:PAD\_RESETNPad:PAD\_CoreVDDNPad:PAD\_IOVDD1N

| Pad: CORNER2 SE | _ |

|-----------------|---|

|-----------------|---|

- Pad: PAD\_CLK S

- Pad: PAD\_CoreVSS S

- Pad: PAD\_IOGND1 S

| Pad: CORNER1   | NE | Pad: CORNER3   | SW |

|----------------|----|----------------|----|

| Pad: PAD_O2    | W  | Pad: PAD_O0    | Е  |

| Pad: PAD_IOVDD | W  | Pad: PAD_IOVSS | Е  |

| Pad: PAD_O3    | W  | Pad: PAD_01    | Е  |

# IO Constraint (3/3)

Pad:CORNERONWPCORNERDGZPad:PAD\_CoreVDDNPVDD1DGZPad:PAD\_CoreVSSSPVSS1DGZPad:PAD\_IOVDDSPVDD2DGZPad:PAD\_IOVSSEPVSS2DGZ

Put a pair of PAD POWER PAD about every 7 I/O pads.

### Starting SOC Encounter

### In /SOC\_tutor directory, type "encounter"

**VLSI System Design**

Layout. 11

# Import Your Design (1/6)

### • Design $\rightarrow$ Design Import

| Design Import                                                                                                                                                                                                                                                                      |                                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| Basic Advanced                                                                                                                                                                                                                                                                     |                                                                               |

| Verilog Netlist:<br>Files: Layout_Design/CHIP.v<br>Top Cell: Auto Assign By User CHIP<br>Timing Libraries:<br>FIII "CHIP?                                                                                                                                                          |                                                                               |

| Cc       Netlist File:       Layout_Design/CHIP.v       Add       -       Netlist Selection         Layout_Design/CHIP.v       Add       -       Filter:       y97/SOC_tutor/Layout_Design/*.v*       Layout_Design/*.v*         Directories:       -       Files:       -       - | Add - Netlist Selection<br>Filter:<br>y97/SOC Choose "CHIP.V"<br>Directories. |

| Choose "Layout"                                                                                                                                                                                                                                                                    |                                                                               |

| Delete                                                                                                                                                                                                                                                                             | Press "Add"                                                                   |

| Qose                                                                                                                                                                                                                                                                               | to add file                                                                   |

## Import Your Design (2/6)

| Design Import     Basic Advanced                                                                                                               | Choose "Library/lib/slow.lib" and<br>"Library/lib/tpz013g3wc.lib"    |

|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| Verilog Netlist:<br>Files: Layout_Design/CHIP.v<br>Top Cell: � Auto Assign 	 By User: CHIP<br>Timing Libraries:                                | Choose "Library/lib/fast.lib" and<br>"Library/lib/tpz013lt.lib"      |

| Max Timing Libraries: Library/lib/slow.lib Library/lib/tpz013g3wc.lib<br>Min Timing Libraries: Library/lib/fast.lib Library/lib/tpz013g3lt.lib | Choose "Library/lib/typical.lib" and<br>"Library/lib/tpz013g3tc.lib" |

| IO Assignment File: Layout_Design/CHIP.ioc                                                                                                     |                                                                      |

| OK Save Load Cancel Help                                                                                                                       |                                                                      |

**VLSI System Design**

Layout. 13

# Import Your Design (3/6)

| X Design Import                                                                                                                                                                                                                                                                                                                                                                                                                                                   | X LEF Files                                                                                                                                         |        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Basic Advanced                                                                                                                                                                                                                                                                                                                                                                                                                                                    | LEF File:                                                                                                                                           | Add 🗾  |

| Verilog Netlist:       Files: Layout_Design/CHIP.v         Top Cell: Auto Assign By User: CHIP         Timing Libraries:         Max Timing Libraries:         Library/lib/slow.lib Library/lib/tpz013g3wc.lib         Min Timing Libraries:         Library/lib/fast.lib Library/lib/tpz013g3lt.lib         Common Timing Libraries:         Library/lib/tpz013g3lt.lib         LEF Files:         Library/lef/tsmc13fsg_8lm_cic.lef Library/lef/antenna_8.lt Li | LEF Files<br>Library/lef/tsmc13fsg_8lm_cic.lef<br>Library/lef/antenna_8.lef<br>Library/lef/tpd013n3_8lm_cic.lef<br>Library/lef/tpz013g3_8lm_cic.lef |        |

| Timing Constraint File: Layout_Design/CHIP.sdc                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                     | Delete |

| IO Assignment File: Layout_Design/CHIP.ioc                                                                                                                                                                                                                                                                                                                                                                                                                        | Close                                                                                                                                               |        |

| <u>O</u> K <u>Save</u> <u>L</u> oad <u>C</u> ancel <u>H</u> elp                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                     |        |

#### **VLSI System Design**

Layout. 14

### Import Your Design (4/6)

| Design Import                                                                                                                                                                                                                                   | CHIP.sdc & CHIP.ioc : |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Basic       Advanced         Verilog Netlist:       Files: Layout_Design/CHIP.v         Top Cell:        Auto Assign        By User: CHIP         Timing Libraries:       Max Timing Libraries: Library/lib/slow.lib Library/lib/tpz013g3wc.lib | Layout_Design/        |

| Min Timing Libraries:       Library/lib/fast.lib Library/lib/tpz013g3lt.lib          Common Timing Libraries:       Library/lib/typical.lib Library/lib/tpz013g3tc.lib                                                                          |                       |

| LEF Files: Library/lef/tsmc13fsg_8lm_cic.lef Library/lef/antenna_8.lef Li<br>Timing Constraint File: Layout_Design/CHIP.sdc                                                                                                                     |                       |

| <u>QK</u> <u>Save</u> Load <u>C</u> ancel <u>H</u> elp                                                                                                                                                                                          |                       |

#### **VLSI System Design**

.

# Import Your Design (5/6)

| Basic Advanced                                                                                                              |                                                                                                                                                                                                         |  |

|-----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Delay Calculation<br>GDS<br>ILM<br>IPO/CTS<br>OpenAccess<br>Power<br>RC Extraction<br>RTL<br>SI Analysis<br>Timing<br>Yield | IPO:<br>Buffer Name/Footprint: buf<br>Delay Name/Footprint: dly1 dly2 dly3 dly4<br>Inverter Name/Footprint: inv<br>CTS:<br>Cell Footprint: clkbuf clkinv<br>Øesign Import<br>Generate Fc Basic Advanced |  |

|                                                                                                                             | Delay Calculation<br>GDS<br>ILM<br>IPO/CTS<br>OpenAccess<br>Power<br>RC Extraction                                                                                                                      |  |

#### **VLSI System Design**

#### Layout. 16

# Import Your Design (6/6)

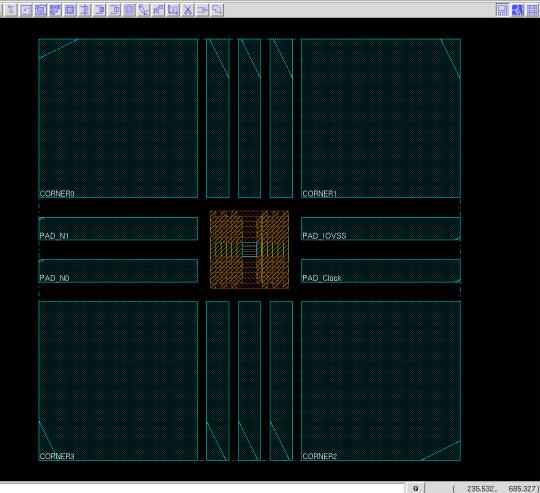

| <u>D</u> esign | <u>E</u> dit | Synthesis | Partitio <u>n</u> | Floorplan | Po <u>w</u> er | <u>P</u> lace | <u>C</u> lock | <u>R</u> oute     | Timing | <u>S</u> I | <u>V</u> erify | Too <u>i</u> s |  |   |  |           |                | <u>H</u> e |

|----------------|--------------|-----------|-------------------|-----------|----------------|---------------|---------------|-------------------|--------|------------|----------------|----------------|--|---|--|-----------|----------------|------------|

|                |              | Q Q 🖉     | <u>い</u><br>日     | <u>n</u>  | v 🔏 •          | <b>1</b>      |               | Ô                 | כ      |            |                |                |  |   |  | Desigr    | ı is:          | In Memory  |

| ★ 🚸            | ů.i. %       |           | P 🔳 🗅             |           | 1 🗸 F          | 4 🗳           | ⋛⊸            | 5.                |        |            |                |                |  |   |  |           | All            | Colors     |

|                |              |           |                   |           |                |               |               |                   |        |            |                |                |  |   |  | 1         |                |            |

|                |              |           |                   |           |                |               |               | X                 | X      |            |                |                |  | X |  | Mo        | idule          |            |

|                |              |           |                   |           |                |               |               |                   |        |            |                |                |  |   |  |           | ick Box        |            |

|                |              |           |                   |           |                |               |               |                   |        |            |                |                |  |   |  | Gu        | nce<br>ide     |            |

|                |              |           |                   |           |                |               |               |                   |        |            |                |                |  |   |  |           | struct         |            |

|                |              |           |                   |           |                |               |               |                   |        |            |                |                |  |   |  |           | gion<br>reen   |            |

|                |              |           |                   |           |                |               |               |                   |        |            |                |                |  |   |  | Ins       | tance          |            |

|                |              |           |                   |           |                |               |               |                   |        |            |                |                |  |   |  | Ne<br>SN  |                |            |

|                |              |           |                   |           |                |               |               |                   |        |            |                |                |  |   |  | P/C       |                |            |

|                |              |           |                   |           |                |               |               |                   |        |            |                |                |  |   |  | Pin       |                |            |

|                |              |           |                   |           |                |               |               |                   |        |            |                |                |  |   |  | Rul<br>VC | ier<br>Congest |            |

|                |              |           |                   |           |                |               |               |                   |        |            |                |                |  |   |  | нс        | ongest         |            |

|                |              |           |                   |           |                |               |               |                   |        |            |                |                |  |   |  | Tex       | kt<br>I. FPlan |            |

|                |              | CORNE     | Ro                |           |                |               |               |                   |        |            | ORNER          |                |  |   |  | Yie       | eld Cell       |            |

|                |              |           |                   |           |                |               |               |                   |        |            |                |                |  |   |  | Yie       | an Map         |            |

|                |              | PAD N     | 1                 |           |                |               |               |                   |        |            | AD IOV         | 55             |  |   |  |           | $\checkmark$   |            |

|                |              | PAD N     | o                 |           |                |               |               |                   |        |            | AD_Clo         | sk             |  |   |  |           |                | L          |

|                |              |           |                   |           |                |               |               |                   |        |            |                |                |  |   |  | į,        | Attribute      | es Value   |

|                |              |           |                   |           |                |               |               |                   |        |            |                |                |  |   |  |           |                |            |

|                |              |           |                   |           |                |               |               |                   |        |            |                |                |  |   |  |           |                |            |

|                |              |           |                   |           |                |               |               |                   |        |            |                |                |  |   |  |           |                |            |

|                |              |           |                   |           |                |               |               |                   |        |            |                |                |  |   |  |           |                |            |

|                |              |           |                   |           |                |               |               |                   |        |            |                |                |  |   |  |           |                |            |

|                |              |           |                   |           |                |               |               |                   |        |            |                |                |  |   |  |           |                |            |

|                |              |           |                   |           |                |               |               |                   |        |            |                |                |  |   |  |           |                |            |

|                |              |           |                   |           |                |               |               |                   |        |            |                |                |  |   |  |           |                |            |

|                |              | N         |                   |           |                |               |               | $\langle \rangle$ |        |            |                |                |  |   |  |           |                |            |

|                |              |           |                   |           |                |               |               |                   |        |            |                |                |  |   |  |           |                |            |

|                |              | CORNE     | R3                |           |                |               |               |                   |        |            | ORNER          | ,              |  |   |  |           |                |            |

|                |              |           |                   |           |                |               |               |                   |        |            |                |                |  |   |  |           |                |            |

Layout. 17

VLSI System Design

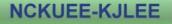

### Global Net Connect (1/2)

### • Floorplan $\rightarrow$ Connect Global Net

| 🗶 Global Net Connections   |                                                                                                 |                     |

|----------------------------|-------------------------------------------------------------------------------------------------|---------------------|

| Connection List            | Power Ground Connection                                                                         |                     |

| VDD:PIN:*.VDD:Module()     | Connect     Pins     VDD     in instances     Nets:                                             | Fill in "VDD"       |

|                            | <ul> <li>↓ Tie High</li> <li>↓ Tie Low</li> </ul>                                               |                     |

|                            | Scope                                                                                           |                     |

|                            | ↓         Under Region: IIX: 0.0         IIy: 0.0         ux: 0.0           ↓         Apply All | ury: 0.0            |

|                            |                                                                                                 | Fill in "VDD"       |

|                            | <ul> <li>Override prior connection</li> <li>Verbose Output</li> </ul>                           |                     |

|                            | Add to List Update                                                                              | Press "Add to List" |

| <u>A</u> pply <u>Check</u> | <u>R</u> eset <u>C</u> lose                                                                     | Help                |

**VLSI System Design**

Layout. 18

# Global Net Connect (2/2)

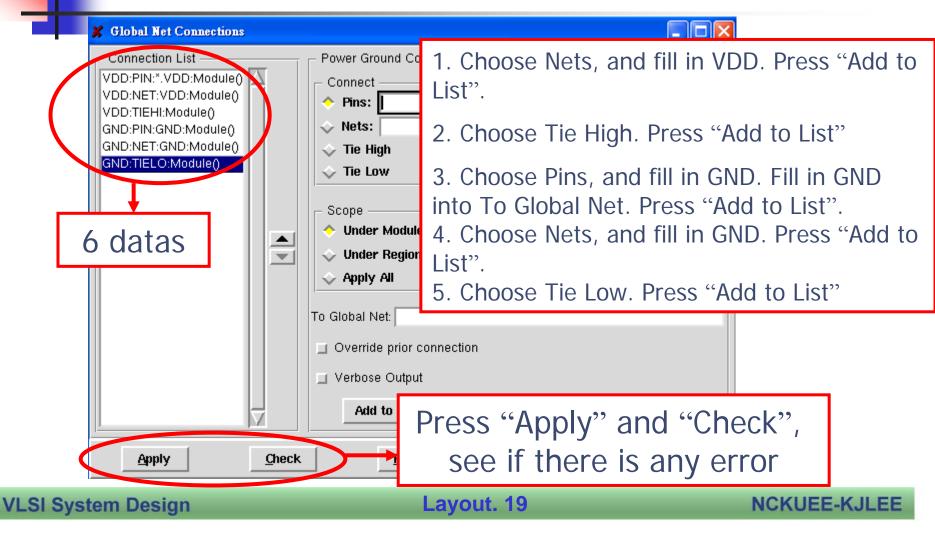

# Specify Floorplan (2/3)

| <u>D</u> esign <u>E</u> dit | Synthesis | Partition | <u>F</u> loorplan | Po <u>w</u> er | <u>P</u> lace                          | Gock | <u>R</u> oute | Timing      | <u>S</u> I | <u>V</u> erify | Too <u>i</u> s |  |         |  |

|-----------------------------|-----------|-----------|-------------------|----------------|----------------------------------------|------|---------------|-------------|------------|----------------|----------------|--|---------|--|

|                             | Q Q &     | 이맘        | <u>n</u>          | ▶ 🛛            | :::::::::::::::::::::::::::::::::::::: |      |               | כ           |            |                |                |  |         |  |

| 🔨 🚸 🛍 🕺                     | 6 🕅 🧱     |           |                   | X 🕹 I          | 4                                      | ∦⊒   | 5,            |             |            |                |                |  |         |  |

|                             |           |           |                   |                |                                        |      |               |             |            |                |                |  |         |  |

|                             |           |           |                   |                |                                        |      |               |             |            |                |                |  |         |  |

|                             |           |           |                   |                |                                        |      |               |             |            |                |                |  |         |  |

|                             | cc        | RNERD     |                   |                |                                        |      |               |             |            | CORNE          | ER1            |  |         |  |

|                             | -         |           |                   |                |                                        |      |               |             |            |                |                |  |         |  |

|                             | PA        | .D_N1     |                   |                |                                        |      |               |             |            | PAD_I          |                |  |         |  |

|                             | PA        | ND NO     |                   |                |                                        |      |               |             |            | PAD_0          | llock          |  |         |  |

|                             |           |           |                   |                |                                        |      |               |             |            |                |                |  |         |  |

|                             |           |           |                   |                |                                        |      |               |             |            |                |                |  |         |  |

|                             |           |           |                   |                |                                        |      |               |             |            |                |                |  |         |  |

|                             |           |           |                   |                |                                        |      |               |             |            |                |                |  |         |  |

|                             |           |           |                   |                |                                        |      |               |             |            |                |                |  |         |  |

|                             |           |           |                   |                |                                        |      |               |             |            |                |                |  |         |  |

|                             |           |           |                   |                |                                        |      |               |             |            |                |                |  |         |  |

|                             |           |           |                   |                |                                        |      |               |             |            | CODNE          | -00            |  |         |  |

|                             | 00        | DRINERS   |                   |                |                                        |      |               | 10000000000 |            | CORNE          | -111-50000     |  | 8000000 |  |

**VLSI System Design**

Layout. 21

# Specify Floorplan (3/3)

■ Design → Save Design

**VLSI System Design**

Layout. 25

( 235.532, 685.327)

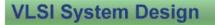

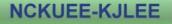

| Powerpla             | n (4/6)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ■ Route → Specia     | X SRoute                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| "VSS" and "VDD" only | Basic Advanced Via Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| "Pad pins" only      | Block pins Pad pins Pad rings Standard cell pins Stripes (unconnected) Het(s): Routing Control Layer Change Control Top layer: M5 Bottom layer: M1 - Straight connections and allow jogging Straight connections only Straight connections only Straight connections and allow jogging Prefer straight with layer change PRC clean Prefer straight with layer change PRC clean Prefer same layer jog Allow layer change Prefer same layer jog Connect to target inside the area only Delete existing routes Generate progress messages Extra config file |

| VLSI System Design   | OK Apply Defaults Cancel Help JLEE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

### Powerplan (5/6)

**VLSI System Design**

# Powerplan (6/6)

■ Design → Save Design

Place (1/2) $Place \rightarrow Standard Cell And Blocks$ Prototyping: fast \_ 🗆 🔼 🕻 Place Full: complete Advanced Basic -Mode 🔶 Full 🔷 Incremental Prototyping Options F Run Timing Driven Placement Reorder Scan Connection -Optimization Optionsnclude Pre–Place Optimization 🔟 Include In-Place Optimization Choose two of these Cancel 0K Apply Defaults Help

**VLSI System Design**

Layout. 29

**VLSI System Design**

Layout. 30

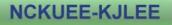

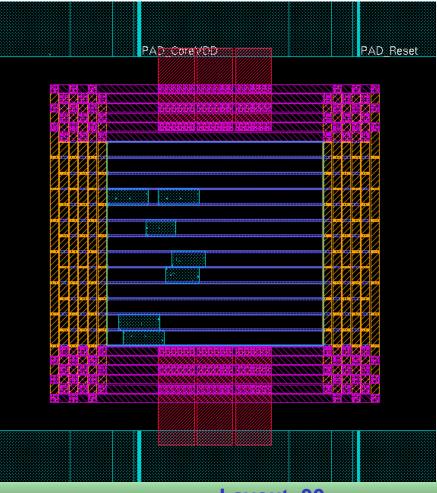

# Trail Route (1/2)

### ■ Route → Trail Route

#### **VLSI System Design**

Layout. 31

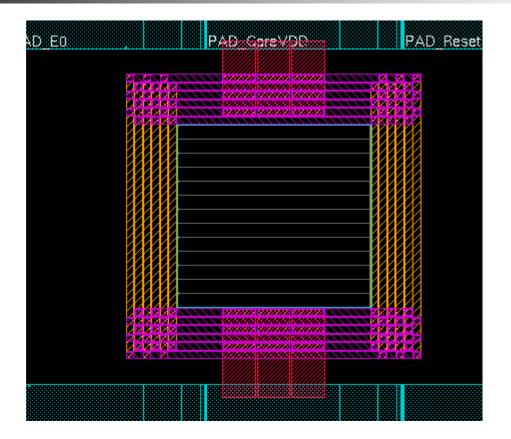

### Trail Route (2/2)

| PAD E0 | PAD Core VDD | PAD_Reset | CORNER1                                 |

|--------|--------------|-----------|-----------------------------------------|

|        |              |           | IOFILLERIE                              |

|        |              |           |                                         |

|        |              |           |                                         |

|        |              |           |                                         |

|        |              |           |                                         |

|        |              |           |                                         |

|        |              |           |                                         |

|        |              |           | PAD IOVS                                |

|        |              |           | 888888888888888888888888888888888888888 |

|        |              |           | IOFILLER                                |

|        |              |           |                                         |

|        |              |           |                                         |

|        |              |           |                                         |

|        |              |           |                                         |

|        |              |           |                                         |

|        |              |           |                                         |

|        |              |           | PAD Clock                               |

|        |              |           | IOFILLER I                              |

|        |              |           |                                         |

|        |              |           |                                         |

**VLSI System Design**

Layout. 32

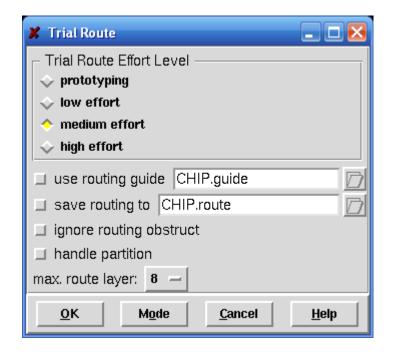

# Trail Route: Time Analysis (2/2)

- Timing  $\rightarrow$  Extract RC, and press OK

- Timing → Timing Analysis, and press OK

- Terminal → Check the Slack

- If there is some negative Timing Slack, you can "Timing → Optimization"

- If still negative, you must synthesis again

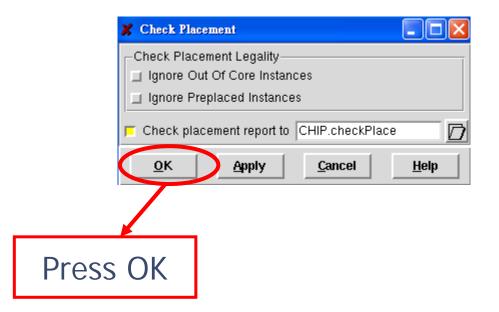

### Check

### ■ Place → Check Placement

**VLSI System Design**

■ Design → Save Design

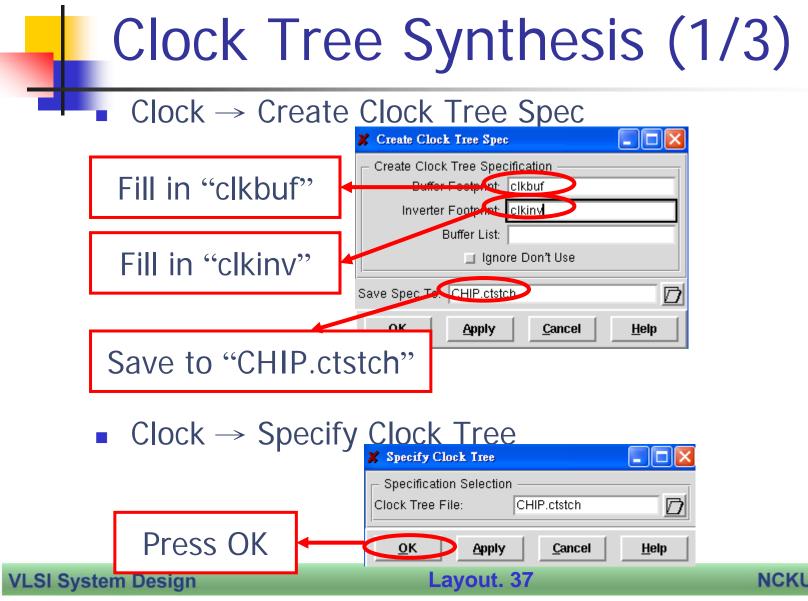

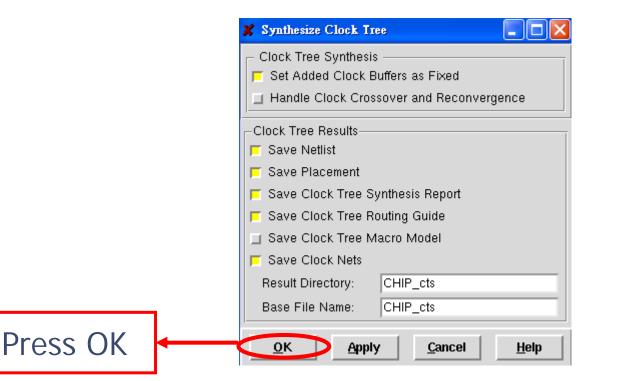

## Clock Tree Synthesis (2/3)

#### Clock $\rightarrow$ Synthesize Clock tree

**VLSI System Design**

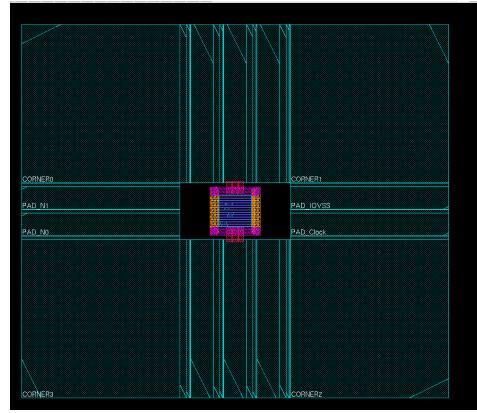

## Clock Tree Synthesis (3/3)

■ Design → Save Design

#### Connect follpower

# ■ Route → Special Route..

| ſ            | Basic Advanced Via Generation                                                                                                                                                                                                                                                                                                                                                                                              | 1.Standard cell pins  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

|              | Net(s): GND VDD                                                                                                                                                                                                                                                                                                                                                                                                            |                       |

|              | Route:<br>Block pins Pad pins Pad rings Standard cell pins Stripes (unc<br>Level shifter pins<br>Net(s):                                                                                                                                                                                                                                                                                                                   | onnected)             |

|              | Routing Control         Layer Change Control         Top layer:       M5         Straight connections and allow jogging       Straight connections only         Straight connections and allow jogging       Straight connections only         Prefer straight with layer change       DRC clean         Prefer different layer jog       Allow layer change         Prefer same layer jog       Straight connections only | me layer routing only |

|              | □ Area         Draw           ×1:         ×1:           ×2:         Y2:                                                                                                                                                                                                                                                                                                                                                    |                       |

| 2.pass ok    | Connect to target inside the area only  Delete existing routes                                                                                                                                                                                                                                                                                                                                                             |                       |

|              | Generate progress messages Extra config file                                                                                                                                                                                                                                                                                                                                                                               |                       |

| _SI System E | <u>OK</u> <u>Apply</u> <u>Defaults</u> <u>Cancel</u>                                                                                                                                                                                                                                                                                                                                                                       |                       |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                            |                       |

#### Connect follpower

|    | PAD   | PAD_Reset                      |

|----|-------|--------------------------------|

|    |       | S S S S REAL & REPORT A REAL A |

|    |       |                                |

|    |       |                                |

|    |       |                                |

|    |       |                                |

|    |       |                                |

|    |       |                                |

|    |       |                                |

|    |       |                                |

| In | Lavou | if <u>41</u>                   |

NCKUEE-KJLEE

**VLSI System Design**

#### Add io filler

Type "source addIoFiller\_tpz.cmd" in terminal

**VLSI System Design**

Layout. 42

## NanoRoute (1/2)

#### • Route $\rightarrow$ NanoRoute $\rightarrow$ Route..

|                        | X NanoRoute                                                                           |              |

|------------------------|---------------------------------------------------------------------------------------|--------------|

|                        | Mode<br>Global Route<br>Detail Route Start Iteration default End Iteration default    |              |

|                        | Concurrent Routing Features<br>Fix Antenna Insert Diodes Diode Cell Name Fill Cells   |              |

| Choose two             | Congestion Timing Timing Driver Effort 0 Congestion SI SI Driven Effort pormal        |              |

| Choose two<br>of these | Post Route SI SI Victim File                                                          |              |

|                        | Selected Nets Only Regenerate Tracks Bottom Layer default Top Layer defa<br>ECO Route | ult          |

|                        | Area Route Area                                                                       | te           |

|                        | Auto<br>Multi<br>Supe Press "Attribute"                                               |              |

|                        | <u>QK</u> <u>Apply</u> <u>Attribute</u> <u>Save</u> <u>Load</u> <u>Cancel</u>         | <u>+</u> elp |

**VLSI System Design**

Layout. 43

# NanoRoute (2/2)

#### NanoRoute/Attributes Net Attributes Net Type(s) Clock Nets External Nets Critical Nets Selected Nets Ne Name(s Choose two 🐟 TRUE 🐟 FALSE 🔶 ASIS Top Layer ASIS Bottom Layer ASIS of these 🔷 TRUE 🔷 FALSE 🔶 ASIS 10 Weight Spacing Ŧ TRUE 🔪 FALSE 🔷 ASIS Avoid Detour Shield Net(s) ASIS TRUE 🔷 FALSE 🔶 ASIS SI Prevention Choose 1 Nondefault Ru Fill in 10 SI Post Route Fix 🐟 🖪 RUE 🐟 FALSE 🔷 ASIS Pattern AOIO **± OK** Select Apply Cancel Help Choose TRUE

**VLSI System Design**

Layout. 44

## Timing Analysis (1/4)

■ Timing → Specify Analysis Condition → Specify Operating Condition/PVT

|                                                                | Uperating to | ondition     |               | Temp           | Proc | Volt         |

|----------------------------------------------------------------|--------------|--------------|---------------|----------------|------|--------------|

|                                                                | Timing Libr  | ary: umc18   | 3io3∨5∨_slow  |                |      |              |

|                                                                | W            |              |               | 125.0          | 1.0  | 3.0          |

|                                                                | umc18io3v5v  | _slow/%NOM_F | PVT           | 125.0          | 1.0  | 1.62         |

|                                                                | Timing Libr  | ary: slow    |               |                |      |              |

|                                                                | slow         |              |               | 125.0          | 1.0  | 1.62         |

|                                                                | slow/%NOM_P  | VT           |               | 125.0          | 1.0  | 1.62 -       |

| ecify Operating Condition                                      | Timing Libr  | ary: umc18   | }io3v5v_fast  |                |      |              |

| $\frown$                                                       | b            |              |               | 0.0            | 1.0  | 3.6          |

| in min                                                         | umc18io7u5u  |              | * 1           | 0.0            | 1.0  | 1.98         |

|                                                                | Timing Libr. | ary: fast    |               |                |      |              |

| Operating Condition                                            |              |              |               |                |      |              |

| Timing Library: umc18io3v5v_fas                                |              |              | 1             |                | 1    |              |

| b                                                              | <u>о</u> к   |              | <u>R</u> eset | <u>C</u> ancel |      | <u>H</u> elp |

| umc18io3v5v_fast/%NOM_PVT                                      | 0.0          | ±.0 -        | 1.90          |                |      |              |

| Timing Library: fast                                           |              |              |               |                |      |              |

| fast                                                           | 0.0          | 1.0          | 1.98          |                |      |              |

| fast/%NOM_PVT                                                  | 0.0          | 1.0          | 1.98 -        |                |      |              |

| Timing Library: umc18io3v5v_slo                                |              |              |               |                |      |              |

|                                                                | 125.0        | 1.0          | 3.0           |                |      |              |

|                                                                |              |              |               |                |      |              |

| W<br>I <u>me10:2757_sicm/WHCH_PV</u> T<br>Timing Library: slow | 125.0        | 1.0          | 1.62          |                |      |              |

**VLSI System Design**

Layout. 45

| Timing Ar                                                                                        | halysis (2/4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1)                |

|--------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| <ul> <li>Timing → Specify<br/>Extraction Mode</li> <li>Choose "Assume<br/>Metal Fill"</li> </ul> | RC Extraction Mode         Mode       Defaul       Detail         I ssume Metal Fill       1.0         Special Net       Image: Creative of the system | noose "Detail"    |

| LSI System Design                                                                                | <u>OK</u> <u>Apply</u> <u>Cancel</u><br>Layout. 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Help NCKUEE-KJLEE |

N

#### Timing Analysis (3/4)

- Timing  $\rightarrow$  Extract RC  $\rightarrow$  OK

- Timing → Timing Analysis

| -Design Stage                              |                                                                                                                |                | ÷1 |

|--------------------------------------------|----------------------------------------------------------------------------------------------------------------|----------------|----|

| ◇ Pre-Place ◇ Pr                           | re-CTS 💠 Post-CTS 🔷 Post-I                                                                                     | Route Sign-Off | 8  |

| Analysis Type                              |                                                                                                                |                |    |

| Setup<br>Include SI                        | bid                                                                                                            |                |    |

|                                            |                                                                                                                |                |    |

| -Reporting Options-                        |                                                                                                                |                |    |

| Use Existing Ext                           | raction and Timing Data                                                                                        |                |    |

|                                            |                                                                                                                |                |    |

| Number of Paths:                           | 50                                                                                                             |                |    |

| Number of Paths:<br>Report file(s) Prefix: | presentation of the second |                |    |

**VLSI System Design**

## Timing Analysis (4/4)

- Terminal → Check the Slack

- If there is some negative Timing Slack, you can "Timing → Optimization"

- If still negative, you must synthesis again

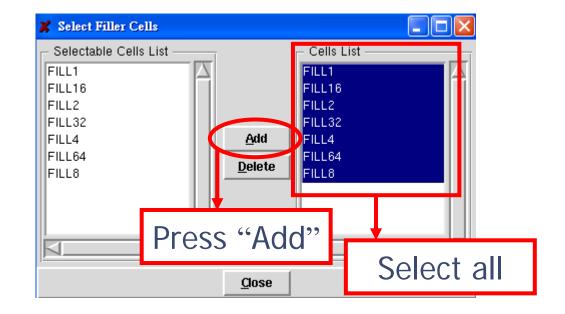

# Add Filler (1/2)

- Place  $\rightarrow$  Filler  $\rightarrow$  Add..

- In Add Filler Form, press "select"

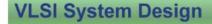

## Add Filler (2/2)

**VLSI System Design**

Layout. 50

#### Check

- Verify → Connectivity

- Verify → Geometry

- Place → Check placement

#### Save Design

- Step 1. Design → Save Design

- File name : finish.enc

- Step 2. Design  $\rightarrow$  Save  $\rightarrow$  GDS

- Output Stream File : CHIP.gds

- Map File : streamOut.map

- Units 2000 → 1000

- Step 3. Design  $\rightarrow$  Save  $\rightarrow$  Netlist

- File name : CHIP\_lvs.v

- Step 4. Design  $\rightarrow$  Save  $\rightarrow$  DEF

- File name : CHIP.def

- Step 5. Design  $\rightarrow$  Exit

#### **Prepare for Verification**

Stream In Design

Stream Out Design

# Stream In Design (1/3)

- Copy CHIP.gds to directory icfb

- Source the file

- source /usr/cad/mentor/CIC/calibre.cshrc

- icfb &

- Workstation

- /Library/icfb directory

## Stream In Design (2/3)

#### • File $\rightarrow$ Import $\rightarrow$ Stream

| 🗶 Virtu    | oso?Stream   | In         |          |                                   |                        |

|------------|--------------|------------|----------|-----------------------------------|------------------------|

| ок         | Cancel       | Defaults   | Apply    |                                   | Help                   |

| User-De    | efined Data  | And Option | ns (     | ser-Defined Data Options Set Fas  | t Options              |

| Templat    | e File       | Load       | Save     |                                   | CHIP.gds               |

| Run Dire   | ectory       |            |          |                                   |                        |

| Input File | e            |            | <b>(</b> | CHIP.gds                          | CHIP                   |

| Top Cell   | Name         |            | (        | CHIP                              |                        |

| Output     |              |            |          | 🔷 Opus DB 🔷 ASCII Dump 🗸 TechFile | -                      |

| Library I  | Name         |            |          | CHIP                              |                        |

| ASCII Te   | echnology Fi | ile Name   | <        | Virtuoso4.4_0.13um_Ver2.1a.1.tf   |                        |

| Scale UI   | U/DBU        |            |          | 0.00100000                        |                        |

| Units      |              |            |          | ◆ micron ◇ millimeter ◇ mil       |                        |

| Process    | Nice Value   | 0-20       |          | virtuoso                          | 4.4_0.13um_Ver2.1a.1.t |

| Error Me   | essage File  |            |          | PIPO.LOG                          |                        |

**VLSI System Design**

Layout. 55

## Stream In Design (3/3)

- File  $\rightarrow$  Import  $\rightarrow$  Stream

- Input File: tpz013g3.gds (the file is in the GDSII directory)

- Top Cell Name: empty

- Press OK

- File  $\rightarrow$  Import  $\rightarrow$  Stream

- Input File: tsmc13gfsg\_fram.gds (the file is in the GDSII directory)

- Top Cell Name: empty

- Press OK

#### Stream Out Design

#### • File $\rightarrow$ Export $\rightarrow$ Stream

| 🗶 Virtuos  | so?Stream | Out       |       |                                                        |                  | ×  |                    |

|------------|-----------|-----------|-------|--------------------------------------------------------|------------------|----|--------------------|

| ОК         | Cancel    | Defaults  | Apply |                                                        | He               | lþ |                    |

| User-Def   | īned Data | And Optio | ns U  | ser-Defined Data Options                               | Set Fast Options |    |                    |

| Template   | File      | Load      | Save  | ¥                                                      |                  | C  | HIP                |

|            |           |           |       | Library Browser                                        |                  |    |                    |

| Run Direc  | tory      |           |       | Ĭ                                                      |                  |    | HIP                |

| Library Na | ame       |           |       | CHIP                                                   |                  |    |                    |

| Top Cell N | lame      |           |       | CHIP                                                   |                  |    | vout               |

| View Nam   | ne        |           |       | layout                                                 |                  | Id | yout               |

| Output     |           |           |       | ♦ Stream DB ◇ ASCII Dump                               |                  |    |                    |

| Output Fil | le        |           |       | CHIP.gds2                                              |                  |    | <sup>p</sup> .gds2 |

| Compress   | sion      |           |       | $\diamond$ gzip $\diamond$ bzip2 $\diamond$ compress 🔶 | none             |    |                    |

| Scale UU   | /DBU      |           |       | 0.00100000                                             |                  |    |                    |

| Units      |           |           |       | ◆ micron ◇ millimeter ◇ mil                            |                  |    |                    |

| n Desigr   | n         |           |       | Layout. 57                                             |                  | NC | KUEE-K             |

# Design Check DRC LVS

#### DRC

- Copy CHIP.gds2 from directory icfb to verify/drc

- Edit file Calibre-drc-cur

- Replace Layout PATH to Layout PATH "CHIP.gds2"

- Replace Layout PRIMARY to Layout PRIMARY "CHIP"

- Execute Calibre

- calibre -drc -hier Calibre-drc-cur

- Check result

- Open file "drc.summary", it should be no errors

**VLSI System Design**

Layout. 59

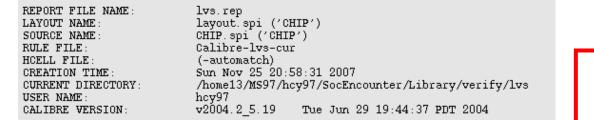

LVS (1/3)

- Copy CHIP.gds2 to directory LVS

- Copy CHIP\_lvs.v to directory LVS

- Transform CHIP\_lvs.v to spice format

- v2lvs -v CHIP\_lvs.v -l tsmc13gfsg\_fram\_lvs.v -o CHIP.spi -s tsmc13gfsg\_fram\_lvs.spi –s1 VDD –s0 GND

LVS (2/3)

- Edit file Calibre-lvs-cur

- Replace SOURCE PRIMARY to SOURCE PRIMARY "CHIP"

- Replace SOURCE PATH to SOURCE PATH "CHIP.spi"

- Replace Layout PRIMARY to Layout PRIMARY "CHIP"

- Replace Layout PATH to Layout PATH "CHIP.gds2"

Execute Calibre

calibre -lvs -spice layout.spi -hier -auto Calibre-lvs-cur

LVS (3/3)

#### Result

#### Check result

#### Open file "lvs.report"

| ## |   |     |   |   |   |    |            |     |   |   |   | ## |

|----|---|-----|---|---|---|----|------------|-----|---|---|---|----|

| ## | С | A L | Ι | в | R | Е  | S          | ΥS  | Т | Ε | М | ## |

| ## |   |     |   |   |   |    |            |     |   |   |   | ## |

| ## |   | L   | ¥ | S |   | RΕ | <b>P</b> 0 | ) R | т |   |   | ## |

| ## |   |     |   |   |   |    |            |     |   |   |   | ## |

OVERALL COMPARISON RESULTS

If there is a smile, the result of LVS is correct

**VLSI System Design**

Layout. 63